# A Gate-All-Around $In_2O_3$ Nanoribbon FET With Near 20 mA/ $\mu$ m Drain Current

Zhuocheng Zhang<sup>®</sup>, Zehao Lin<sup>®</sup>, Pai-Ying Liao<sup>®</sup>, Vahid Askarpour, Hongyi Dou, Zhongxia Shang, Adam Charnas<sup>®</sup>, Mengwei Si<sup>®</sup>, *Member, IEEE*, Sami Alajlouni<sup>®</sup>, Ali Shakouri, Haiyan Wang, Mark Lundstrom<sup>®</sup>, *Life Fellow, IEEE*, Jesse Maassen<sup>®</sup>, and Peide D. Ye<sup>®</sup>, *Fellow, IEEE*

Abstract—In this work, we demonstrate atomic-layerdeposited (ALD) single-channel indium oxide (In<sub>2</sub>O<sub>3</sub>) gateall-around (GAA) nanoribbon field-effect transistors (FETs) in a back-end-of-line (BEOL) compatible process. A maximum on-state current (I<sub>ON</sub>) of 19.3 mA/ $\mu$ m (near 20 mA/ $\mu$ m) and an on/off ratio of 10^6 are achieved in an In<sub>2</sub>O<sub>3</sub> GAA nanoribbon FET with a channel thickness (T<sub>IO</sub>) of 3.1 nm, channel length (L<sub>ch</sub>) of 40 nm, channel width (W<sub>ch</sub>) of 30 nm and dielectric HfO2 of 5 nm. Short-pulse measurements are applied to mitigate the self-heating effect induced by the ultra-high drain current flowing in the ultra-thin channel layer. The record high drain current obtained from an In<sub>2</sub>O<sub>3</sub> FET is about one order of magnitude higher than any conventional single-channel semiconductor FETs. This extraordinary drain current and its related on-state performance demonstrate that ALD In<sub>2</sub>O<sub>3</sub> is a promising oxide semiconductor channel with great opportunities in BEOL compatible monolithic 3D integration.

Index Terms—Indium oxide, amorphous oxide semiconductor, gate-all-around nanoribbon transistor, BEOL compatible, atomic layer deposition.

### I. INTRODUCTION

MORPHOUS oxide semiconductors are widely investigated and applied as thin-film transistor channels for display applications over the past decades [1], [2], [3]. Very recently, they are explored for back-end-of-line

Manuscript received 20 July 2022; revised 14 September 2022; accepted 20 September 2022. Date of publication 26 September 2022; date of current version 24 October 2022. This work was supported in part by the Semiconductor Research Corporation (SRC) nCore Innovative Materials and Processes for Accelerated Compute Technologies (IMPACT) Center, in part by the Defense Advanced Research Projects Agency (DARPA)/SRC Joint University Microelectronics Program (JUMP) Applications and Systems Driven Center for Energy-Efficient Integrated NanoTechnologies (ASCENT) Center, in part by the Air Force Office of Scientific Research Council of Canada (NSERC), and in part by the Compute Canada. The review of this letter was arranged by Editor P. Barquinha. *(Corresponding author: Peide D. Ye.)*

Zhuocheng Zhang, Zehao Lin, Pai-Ying Liao, Adam Charnas, Mengwei Si, Sami Alajlouni, Ali Shakouri, Mark Lundstrom, and Peide D. Ye are with the Elmore Family School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA (e-mail: yep@purdue.edu).

Vahid Askarpour and Jesse Maassen are with the Department of Physics and Atmospheric Science, Dalhousie University, Halifax, NS B3H 4R2, Canada.

Hongyi Dou, Zhongxia Shang, and Haiyan Wang are with the School of Materials Science and Engineering, Purdue University, West Lafayette, IN 47907 USA.

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2022.3210005.

Digital Object Identifier 10.1109/LED.2022.3210005

(BEOL) compatible transistor channels for monolithic 3D integration [4], [5], [6], [7]. Among these materials, atomic layer deposited (ALD)  $In_2O_3$  shows excellent transport properties with mobility beyond 100 cm<sup>2</sup>/V · s and its field-effect transistors (FETs) exhibit remarkable performance including large on-state current ( $I_{ON}$ ) over 2-3 mA/ $\mu$ m in both depletion and enhancement-mode operation, on/off ratio up to  $10^{17}$ , sub-threshold swing (SS) as low as 63 mV/dec, and high stability in H<sub>2</sub> environment [8], [9], [10], [11], [12], [13], [14]. Mean-while, the ALD technique offers wafer-scale film synthesis, accurate thickness control, smooth surface, high conformity and uniformity on 3D structures and a low thermal budget process below 300 °C [9], [10], [11], [12], [13], [14].

In this work, scaled single-channel In<sub>2</sub>O<sub>3</sub> nanoribbon FETs with gate-all-around (GAA) structure and various channel length (L<sub>ch</sub>) of 40 nm  $- 1 \mu$ m and channel width (W<sub>ch</sub>) of 30 nm – 1  $\mu$ m are fabricated under BEOL compatible conditions. On-current (I<sub>ON</sub>) is enhanced to 4.3 mA/ $\mu$ m at drain voltage of 1 V in a device with L<sub>ch</sub> of 40 nm and W<sub>ch</sub> of 1  $\mu$ m compared to the previous bottom or top-gated ALD  $In_2O_3$  FETs [9], [13]. To resolve the self-heating issue due to the ultrahigh current in the ultrathin channel, the channel width scaling and short-pulse measurements are applied. The self-heating effect is mitigated significantly after these two approaches and a maximum I<sub>ON</sub> of 19.3 mA/ $\mu$ m is observed at a drain voltage of 1.7 V in a 30 nm wide nanoribbon FET by pulsed I-V measurements. This extraordinary drain current density is the highest ever obtained from a single-channel transistor [14].

## II. EXPERIMENTS

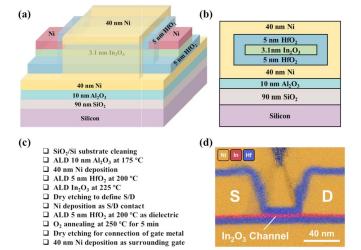

Fig. 1(a) and 1(b) show the device schematic of a singlechannel In<sub>2</sub>O<sub>3</sub> GAA FET in 3D model and cross-section view in source/drain direction respectively. A fabrication process flow is presented in Fig. 1(c). The device fabrication started with solvent cleaning of p+ Si substrate with 90 nm thermally grown SiO<sub>2</sub>. Then, 10 nm Al<sub>2</sub>O<sub>3</sub> was grown by ALD at 175 °C to obtain a smooth surface and a bi-layer photoresist lithography process was applied for the sharp lift-off of Ni by electron-beam evaporation as the bottom gate metal. Next, 5 nm HfO<sub>2</sub> bottom dielectric was grown by ALD at 200 °C, using [(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Hf (TDMAHf) and H<sub>2</sub>O as Hf and O precursors. 3.1 nm In<sub>2</sub>O<sub>3</sub> was grown by ALD at 225 °C with (CH<sub>3</sub>)<sub>3</sub>In (TMIn) and H<sub>2</sub>O as In and O precursors. N<sub>2</sub> was used as carrier gas at a flow rate of 40 sccm and the base pressure is 1500 mTorr. The film thickness was confirmed by transmission electron microscopy (TEM) and ellipsometry. Channel isolation was done by dry etching (BCl<sub>3</sub>: 15 sccm;

0741-3106 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. Device schematic of an  $In_2O_3$  GAA nanoribbon FET with  $T_{IO}$  of 3.1 nm and dielectric of 5 nm HfO<sub>2</sub> in (a) 3D model (b) cross-section view in S/D direction. (c) Fabrication process flow of the  $In_2O_3$  GAA nanoribbon FETs. (d) EDS cross-section image of an  $In_2O_3$  GAA FET with  $L_{ch}$  of 40 nm.

Ar: 60 sccm; pressure: 0.6 Pa) and Ni was deposited to serve as the source/drain electrodes, patterned by electron beam lithography. A top dielectric of 5 nm HfO<sub>2</sub> was then grown by ALD at 200 °C to wrap the whole In<sub>2</sub>O<sub>3</sub> channel followed by 5 min O<sub>2</sub> annealing at 250 °C. Finally, the gate metal was surrounded by e-beam evaporation of 40 nm Ni with dry etching first to connect the top and bottom gates. Fig. 1(d) shows the energy dispersive x-ray spectroscopy (EDS) cross-section image of an In<sub>2</sub>O<sub>3</sub> GAA FET with L<sub>ch</sub> of 40 nm. As can be seen, single layer In<sub>2</sub>O<sub>3</sub> with channel thickness (T<sub>IO</sub>) of 3.1 nm is surrounded by 5 nm HfO<sub>2</sub> dielectric and 40 nm Ni gate stack. 3.1 nm thick In<sub>2</sub>O<sub>3</sub> layer was chosen to realize the record high drain current of the devices. Even thicker In<sub>2</sub>O<sub>3</sub> layer leads to the fact that the devices cannot fully pinch-off since the thickness is beyond the maximum depletion width of the  $In_2O_3$  layer. Notice that the whole fabrication process has a BEOL compatible low thermal budget of 250 °C.

#### **III. RESULTS AND DISCUSSIONS**

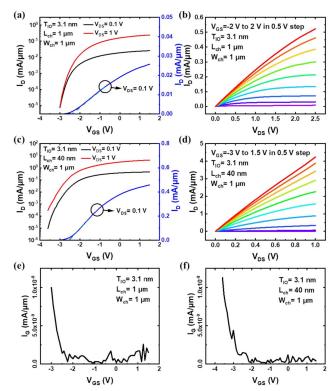

Fig. 2(a) and 2(b) present the transfer and output characteristics of a typical In<sub>2</sub>O<sub>3</sub> GAA FET with L<sub>ch</sub> of 1 µm and W<sub>ch</sub> of 1  $\mu$ m. Well-behaved switching characteristics with on/off ratio over  $10^4$  and a clear drain current saturation at large drain voltage (V<sub>DS</sub>) are observed. I<sub>ON</sub> reaches 500  $\mu$ A/ $\mu$ m at V<sub>DS</sub> of 2.5 V. All I<sub>ON</sub> are simply normalized by W<sub>ch</sub> since the channel thickness T<sub>IO</sub> is much smaller than W<sub>ch</sub>. The gate leakage current (I<sub>G</sub>) is at the level of  $10^{-9}$  mA/ $\mu$ m and the on/off ratio is limited by the off-state current (IOFF) that can be probed. Further increasing negative gate bias will lead to the dielectric hard breakdown of 5nm HfO<sub>2</sub>. Fig. 2(c) and 2(d) show the transfer and output characteristics of a short channel  $In_2O_3$  GAA FET with  $L_{ch}$  of 40 nm and  $W_{ch}$  of 1  $\mu$ m. A maximum I<sub>ON</sub> of 4.3 mA/ $\mu$ m is achieved at V<sub>DS</sub> of 1 V. Further increasing  $V_{DS}$  results in the unstable devices due to ultrahigh current density induced Joule heating in the nanometer-thin In<sub>2</sub>O<sub>3</sub> channel [13], [15]. V<sub>T</sub> is near constant for devices with different L<sub>ch</sub> and maximum transconductance (g<sub>m</sub>) exceeds  $10^3 \mu$ S/ $\mu$ m due to 5 nm thin HfO<sub>2</sub> dielectric. The relatively negative V<sub>T</sub> is attributed to the large electron carrier concentration in the channel and the Fermi level  $(E_F)$  located

Fig. 2. (a) Transfer and (b) output characteristics of a typical In<sub>2</sub>O<sub>3</sub> GAA nanoribbon FET with L<sub>ch</sub> of 1  $\mu$ m and W<sub>ch</sub>of 1  $\mu$ m, showing saturation at large V<sub>DS</sub>. (c) Transfer and (d) output characteristics of a typical In<sub>2</sub>O<sub>3</sub> GAA FET with L<sub>ch</sub> of 40 nm and W<sub>ch</sub>of 1  $\mu$ m, showing maximum I<sub>ON</sub> of 4.3 mA/ $\mu$ m at V<sub>DS</sub> = 1 V. The worse gate control in the short channel device such as degraded drain-induced-barrier-lowing (DIBL) and sub-threshold voltage (SS) are due to the short-channel effect. Gate leakage current (I<sub>G</sub>) of In<sub>2</sub>O<sub>3</sub> GAA FETs with (e) L<sub>ch</sub> of 1  $\mu$ m and W<sub>ch</sub>of 1  $\mu$ m.

highly above the conduction band edge ( $E_C$ ). Further lowering  $In_2O_3$  thickness will enhance the bandgap due to the quantum confinement effect and shift  $E_C$  toward  $E_F$ . The reduction of carrier density results a positive shift of  $V_T$  and a decrease of drain current, which can be considered as a tradeoff between channel thickness and maximum drain current [8].

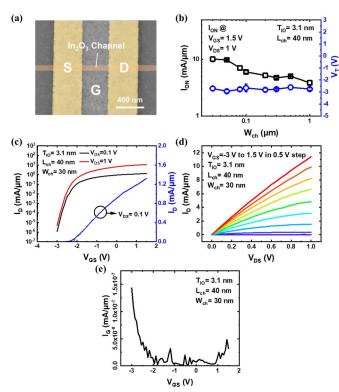

Channel width scaling of the In<sub>2</sub>O<sub>3</sub> ribbon is also investigated. Fig. 3(a) illustrates a false-color top-view scanning electron microscope (SEM) image of a fabricated GAA In<sub>2</sub>O<sub>3</sub> nanoribbon FET with a W<sub>ch</sub> of 50 nm. Similar electrical measurements are performed and the extracted ION versus Wch of different devices from 1  $\mu$ m down to 30 nm is plotted in Fig. 3(b) with SS of 100-120 mV/dec. It is surprising that I<sub>ON</sub> becomes approximately three times larger as the channel narrows with no obvious V<sub>T</sub> shift. Two factors are accounted for such current enhancement. First, the electric field induces a higher carrier density at the channel edge due to the GAA geometry and the edge gradually takes a larger portion of the conductance in the channel width scaling. Etched In<sub>2</sub>O<sub>3</sub> ribbon edges might lead to a charge neutrality level (CNL) located even deeper inside the conduction band, thereby enhancing edge conduction. Second, better heat dissipation is realized due to a larger perimeter to area ratio in a narrower ribbon. Fig. 3(c) and 3(d) present the transfer and output characteristics of an In<sub>2</sub>O<sub>3</sub> GAA nanoribbon FET with L<sub>ch</sub> of 40 nm and  $W_{ch}$  of 30 nm. A maximum I<sub>ON</sub> of 11.4 mA/ $\mu$ m is achieved at a V<sub>DS</sub> of 1 V. The narrow ribbon structure leads to the enhanced on-state performance as shown in Fig. 3(d) and also

Fig. 3. (a) False-color top-view SEM image of an In<sub>2</sub>O<sub>3</sub> GAA nanoribbon FET with W<sub>ch</sub>of 50 nm. (b) I<sub>ON</sub> and V<sub>T</sub> of the In<sub>2</sub>O<sub>3</sub> GAA nanoribbon FETs under channel width scaling from 1  $\mu$ m down to 30 nm. Each point is from at least 3 devices. (c) Transfer and (d) output characteristics of a typical In<sub>2</sub>O<sub>3</sub> GAA nanoribbon FET with L<sub>ch</sub> of 40 nm and W<sub>ch</sub>of 30 nm, showing maximum I<sub>ON</sub> of 11.4 mA/ $\mu$ m at V<sub>DS</sub> = 1 V. (e) I<sub>G</sub> of In<sub>2</sub>O<sub>3</sub> GAA FET with L<sub>ch</sub> of 40 nm and W<sub>ch</sub> of 30 nm.

the improved off-state performance as shown in Fig. 3(c) due to the GAA structure and a better gate control, in contrast to the off-state performance of a wider channel device presented in Fig. 2(c).

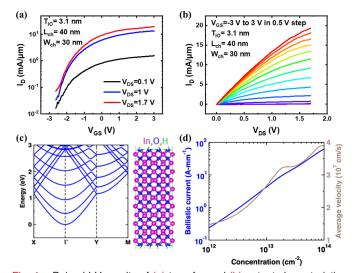

To further probe the potential of the device performance, a pulsed I-V measurement is implemented. A data averaging time of 500 ns,  $V_{GS}$  and  $V_{DS}$  pulse width of 1  $\mu$ s and pulse period of 100 ms are set to minimize the self-heating effect and improve device reliability. Fig. 4(a) and Fig. 4(b) present the pulsed transfer and output characteristics of an In<sub>2</sub>O<sub>3</sub> GAA nanoribbon FET with L<sub>ch</sub> of 40 nm and W<sub>ch</sub> of 30 nm. A record high I<sub>ON</sub> of 19.3 mA/ $\mu$ m is achieved at V<sub>DS</sub> of 1.7 V, demonstrating the remarkable current carrying capacity of ALD In<sub>2</sub>O<sub>3</sub>. The off-state current in the transfer curve is limited by the resolution of the pulsed I-V setup while a real on/off ratio over  $10^6$  is shown in Fig. 3(c) in DC measurements. The thermal time constant of this scaled device is around tens of nanoseconds since the two sets of data measured by DC and pulse setup can merge perfectly, indicating the thermal equilibrium state is achieved within the pulse width of 1  $\mu$ s.

DFT simulations of a 3.0 nm thick slab of single crystal  $In_2O_3$  were performed to study its electronic properties [16], [17]. Fig. 4(c) shows the band structure of the conduction states.  $In_2O_3$  has simple electronic bands, with a single zone-centered band up to 0.5 eV, in contrast to most of III-V compound semiconductors such as GaAs which possess a satellite band near  $E_C$ . High electron density in  $In_2O_3$ enables  $E_F$  to occupy high energy states in the conduction

Fig. 4. Pulsed I-V results of (a) transfer and (b) output characteristics of an  $In_2O_3$  GAA FET with  $L_{ch}$  of 40 nm and  $W_{ch}$  of 30 nm, showing maximum  $I_{ON}$  of 19.3 mA/ $\mu$ m. (c) DFT band structure of 3.0 nm thick  $In_2O_3$  slab, with the lowest conduction band having an effective mass of 0.19 m<sub>0</sub>. (d) Ballistic current density and average electron velocity versus carrier density, from DFT simulation of  $In_2O_3$  slab.

band, where the majority of the conducting electrons have high band velocity. Fig. 4(d) presents the ideal ballistic transport properties, including the ballistic current density and average electronic velocity, versus carrier concentration. The ultra-high drain current is a product of high electron density and high average band velocity [17]. First, E<sub>F</sub> in the 3.1 nm-thick  $In_2O_3$  is located deeply in the conduction band, being different from Si or other conventional semiconductors, so that a high carrier density around  $4 \times 10^{13}$  cm<sup>-2</sup> can be achieved. Second, a single conduction band in In<sub>2</sub>O<sub>3</sub> with relatively low effective mass of 0.19 m<sub>0</sub> and density of states leads high E<sub>F</sub> located in conduction band once high carrier density is populated. It leads high band velocity at E<sub>F</sub> and beneficial high average band velocity. The velocity increases rapidly with high carrier concentration is illustrated by the pink curve in Fig. 4(d). A velocity  $> 3 \times 10^7$  cm/s can be achieved with carrier density at the level of  $4 \times 10^{13}$  cm<sup>-2</sup>. These two factors lead to a record high  $I_{ON}$  of 20 mA/ $\mu$ m. Note that this simulation only provides a qualitative guidance of device performance, since it considers an ideal single crystal of In<sub>2</sub>O<sub>3</sub> and the ballistic transport limit. The real devices are much more complicated with an amorphous oxide channel, a channel length longer than the mean free path and non-negligible interface and bulk defects. In addition, further investigation on device reliability is still needed so as to make ALD In<sub>2</sub>O<sub>3</sub> a competitive candidate as a channel material in practical BEOL applications.

## **IV. CONCLUSION**

In summary, single-channel In<sub>2</sub>O<sub>3</sub> GAA nanoribbon FETs are demonstrated in a BEOL compatible process. A record high I<sub>ON</sub> of 19.3 mA/ $\mu$ m is achieved through short-pulse measurements, channel width scaling and improved heat dissipation in smaller devices. This work demonstrates a surprising result in the field of electronic materials and devices that such an amorphous oxide semiconductor can offer the record high current density. ALD In<sub>2</sub>O<sub>3</sub> as a novel channel material shows great promise in monolithic 3D integration.

#### REFERENCES

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, no. 4016, pp. 488–492, Nov. 2004, doi: 10.1038/nature03090.

- [2] K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano, and H. Hosono, "Amorphous oxide semiconductors for high-performance flexible thinfilm transistors," *Jpn. J. Appl. Phys.*, vol. 45, no. 5B, pp. 4303–4308, May 2006, doi: 10.1143/JJAP.45.4303.

- [3] T. Kamiya, K. Nomura, and H. Hosono, "Present status of amorphous In–Ga–Zn–O thin-film transistors," *Sci. Technol. Adv. Mater.*, vol. 11, no. 4, Feb. 2010, Art. no. 044305, doi: 10.1088/1468-6996/11/4/044305.

- [4] S. Li, M. Tian, Q. Gao, M. Wang, T. Li, Q. Hu, X. Li, and Y. Wu, "Nanometre-thin indium tin oxide for advanced highperformance electronics," *Nature Mater.*, vol. 18, no. 10, pp. 1091–1097, Oct. 2019, doi: 10.1038/s41563-019-0455-8.

- [5] M. Si, J. Andler, X. Lyu, C. Niu, S. Datta, R. Agrawal, and P. D. Ye, "Indium–Tin-Oxide transistors with one nanometer thick channel and ferroelectric gating," ACS Nano, vol. 14, no. 9, pp. 11542–11547, Sep. 2020, doi: 10.1021/acsnano.0c03978.

- [6] S. Samanta, K. Han, C. Sun, C. Wang, A. V.-Y. Thean, and X. Gong, "Amorphous IGZO TFTs featuring extremely-scaled channel thickness and 38 nm channel length: Achieving record high G<sub>m,max</sub> of 125 μS/μm at V<sub>DS</sub> of 1 V and I<sub>ON</sub> of 350 μA/μm," in Proc. IEEE Symp. VLSI Technol., Jun. 2020, pp. 1–2.

- [7] W. Chakraborty, B. Grisafe, H. Ye, I. Lightcap, K. Ni, and S. Datta, "BEOL compatible dual-gate ultra thin-body W-doped indiumoxide transistor with ion  $=370 \mu/\mu$ m, SS = 73 mV/dec and I<sub>on</sub>/I<sub>off</sub> ratio >gt 4×109," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2.

- [8] M. Si, Y. Hu, Z. Lin, X. Sun, A. Charnas, D. Zheng, X. Lyu, H. Wang, K. Cho, and P. D. Ye, "Why In<sub>2</sub>O<sub>3</sub> can make 0.7 nm atomic layer thin transistors," *Nano Lett.*, vol. 21, no. 1, pp. 500–506, Jan. 2021, doi: 10.1021/acs.nanolett.0c03967.

- [9] M. Si, Z. Lin, A. Charnas, and P. D. Ye, "Scaled atomic-layerdeposited indium oxide nanometer transistors with maximum drain current exceeding 2 A/mm at drain voltage of 0.7 V," *IEEE Electron Device Lett.*, vol. 42, no. 2, pp. 184–187, Feb. 2021, doi: 10.1109/LED.2020. 3043430.

- [10] M. Si, A. Charnas, Z. Lin, and P. D. Ye, "Enhancement-mode atomiclayer-deposited In<sub>2</sub>O<sub>3</sub> transistors with maximum drain current of 2.2 A/mm at drain voltage of 0.7 V by low-temperature annealing and stability in hydrogen environment," *IEEE Trans. Electron Devices*, vol. 68, no. 3, pp. 1075–1080, Mar. 2021, doi: 10.1109/TED.2021.3053229.

- [11] M. Si, Z. Lin, Z. Chen, and P. D. Ye, "First demonstration of atomiclayer-deposited BEOL-compatible In<sub>2</sub>O<sub>3</sub> 3D fin transistors and integrated circuits: High mobility of 113 cm<sup>2</sup>/V•s, maximum drain current of 2.5 mA/μm and maximum voltage gain of 38 V/V in In<sub>2</sub>O<sub>3</sub> inverter," in *Proc. Symp. VLSI Technol.*, 2021, pp. 1–2.

- [12] A. Charnas, Z. Lin, Z. Zhang, and P. D. Ye, "Atomically thin In<sub>2</sub>O<sub>3</sub> field-effect transistors with 10<sup>17</sup> current on/off ratio," *Appl. Phys. Lett.*, vol. 119, no. 26, Dec. 2021, Art. no. 263503, doi: 10.1063/5.0075166.

- [13] P.-Y. Liao, M. Si, Z. Zhang, Z. Lin, and P. D. Ye, "Realization of maximum 2 A/mm drain current on top-gate atomic-layer-thin indium oxide transistors by thermal engineering," *IEEE Trans. Electron Devices*, vol. 69, no. 1, pp. 147–151, Jan. 2022, doi: 10.1109/TED.2021.3125923.

- [14] M. Si, Z. Lin, Z. Chen, X. Sun, H. Wang, and P. D. Ye, "Scaled indium oxide transistors fabricated using atomic layer deposition," *Nature Electron.*, vol. 5, no. 3, pp. 164–170, Mar. 2022, doi: 10.1038/s41928-022-00718-w.

- [15] P.-Y. Liao, M. Si, Z. Zhang, Z. Lin, and P. D. Ye, "BEOL-compatible, ALD-grown In<sub>2</sub>O<sub>3</sub> top-gate FETs with maximum drain current of 3 A/mm through thermal engineering and pulse measurement," in *Proc. Int. Symp. VLSI Technol., Syst. Appl. (VLSI-TSA)*, Apr. 2022, pp. 1–2.

- [16] P. Giannozzi, S. Baroni, N. Bonini, M. Calandra, R. Car, C. Cavazzoni, D. Ceresoli, G. L. Chiarotti, M. Cococcioni, I. Dabo, A. D. Corso, S. D. Gironcoli, S. Fabris, G. Fratesi, R. Gebauer, U. Gerstmann, C. Gougoussis, A. Kokalj, M. Lazzeri, L. M. Samos, N. Marzari, F. Mauri, R. Mazzarello, S. Paolini, A. Pasquarello, L. Paulatto, C. Sbraccia, S. Scandolo, G. Sclauzero, A. P. Seitsonen, A. Smogunov, P. Umari, and R. M. Wentzcovitch, "QUANTUM ESPRESSO: A modular and open-source software project for quantum simulations of materials," *J. Phys., Condens. Matter*, vol. 21, no. 39, Sep. 2009, Art. no. 395502, doi: 10.1088/0953-8984/21/39/395502.

- [17] Z. Lin, M. Si, V. Askarpour, C. Niu, A. Charnas, Z. Shang, Y. Zhang, Y. Hu, Z. Zhang, P.-Y. Liao, K. Cho, H. Wang, M. Lundstrom, J. Maassen, and P. D. Ye, "A nanometer-thick oxide semiconductor transistor with ultra-high drain current," 2022, arXiv:2205.00357.